|

||||||||||||||||||||||||||||||||||

Voir Ordinateurs

![]()

Zoom sur

une micro-puce

|

LITHOGRAPHIE des puces des circuits intégrés, des

microprocesseurs Technologie 2021: Intel est toujours à 7 nm alors que le

fondeur taïwanais TSMC annonce déjà produire la gravure à 4 nanomètre). En début 2020, AMD maitrise cette technologie

(architecture Ryzen 4000); pas encore pour Intel, lequel cependant domine

toujours le marché. Technologie atteinte en 2018: 7 nm (nanomètres); objectif 5 nm pour 2020/21. |

Anglais: integrated circuit etching. Etching is used in

microfabrication

to chemically remove layers from the surface of a

wafer during manufacturing.

|

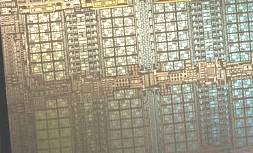

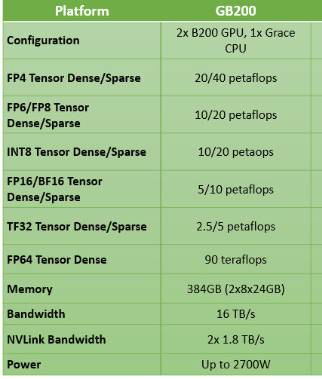

En

Mars 2024, Jensen Huang (CEO Nvidia) dévoile les B200 et GB200, deux

processeurs sur architecture Blackwell ayant pour objectif de doper les

performances IA.

Une

configuration à huit puces H200 Tensor Core GPUs comprenant deux puces GB200

offre 32 peta FLOPS de puissance de calcul. Le plus performant du marché.

Quinze fois plus que la précédente puce de ce constructeur en traitement

d'inférences (= déductions). GPU = Graphics

processing unit. Péta

= 1015 FLOP

= flotting opérations (opérations

flottantes) Source: NVIDIA Blackwell Platform Arrives to Power a New Era of Computing – Newsroom – March 18, 2024 |

Source: NVIDIA

dévoile une nouvelle puce ultra puissante dédiée à l'IA – 19 mars 2024 –

Nerces – Clubic |

ASML – Machines à fabriquer les

semi-condcuteurs

|

Entreprise partie avec trois fois rien il y a 40

ans, depuis Veldhoven, dans la discrète banlieue d’Eindhoven aux Pays-Bas,

s’est forgée "un rôle clef dans une industrie qui pèse aujourd’hui plus

de 600 milliards de dollars par an". L’industrie des puces

électroniques, à la fois les cerveaux et systèmes nerveux de nos smartphones,

téléviseurs, voitures, satellites, scanners médicaux… Demain, de nos

intelligences artificielles (IA). Le dernier produit d’ASML résume d’ailleurs à lui

seul toute la puissance acquise par la firme. Celle "machine la plus

complexe sur Terre" est longue comme un autobus, s’étire sur trois

mètres de haut et presque quatre mètres de large de tuyauteries, de conduits,

de câbles et autres lasers. Cette "imprimante géante" n’est pas

seulement indispensable à la gravure des semi-conducteurs sur des plaquettes

de silicium - la base des puces électroniques. Elle est aussi la seule à

pouvoir opérer ce délicat processus de manière si fine, grâce à la

technologie de lithographie par ondes lumineuses EUV (extrême ultraviolet),

agissant avec une précision de l’ordre du nanomètre

(1/109 m). Le diamètre d’un atome d’hydrogène,

décuplant les performances desdites puces. |

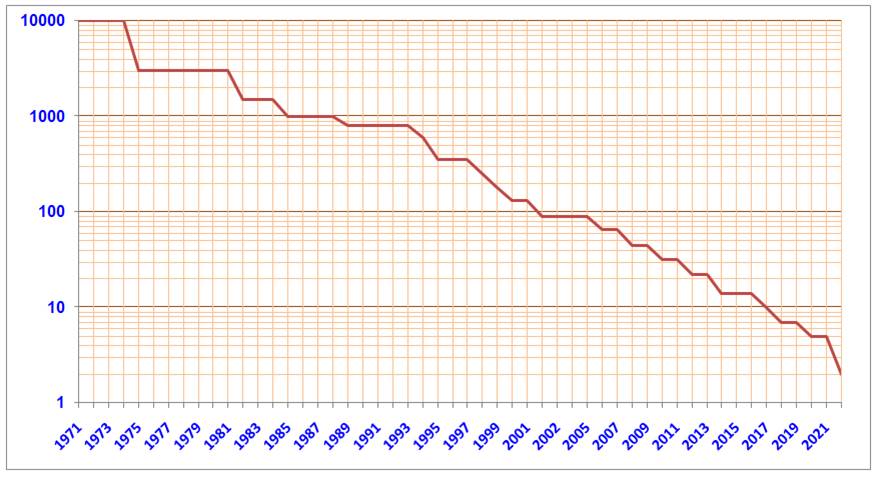

Rappel des facteurs multiplicatifs

Évolution

de la l'épaisseur en nanomètres de la gravure des microprocesseurs

Facteur 5 000 en 50 ans

(de 10µm à 2nm)

Source des données: Microprocessors technology – Wikipédia

Voir Brève

48-949 / Nanotechnologies

|

|

||

|

Apple serait prêt à exploiter les puces 2 nm de TSMC, le fondeur

taïwanais, dès que celles-ci seront prêtes (2025). Comme pour les puces 3 nm, Apple serait le

premier constructeur du marché à exploiter cette nouvelle finesse de gravure. TSMC travaille sur la technologie 1,4 nm à

l'horizon 2027. |

En passant de 3 à 2 nm, les puces sont plus

rapides de 10 à 15%. Rappel: taille du cheveu

humain: 70 000 à 80 000 nm. |

|

Source: Les

Numériques – Nathan Le Gohlisse – 03/03/2024

|

|

||

|

Après que TSMC a annoncé la production de

circuits avec une technologie de trois nanomètres pour 2022, IBM surenchérit

et propose un transistor de seulement deux

nanomètres selon une architecture en millefeuilles qui serait

également adoptée par Samsung et Intel. Ce qui laisse

entendre que les fabricants pourraient intégrer 50 milliards de transistors sur une puce ! |

Les inventeurs s'attendent à un gain en termes de

performances proche de 45% et une consommation d'énergie divisée par quatre,

soit quatre fois plus d'autonomie pour les appareils mobiles. |

|

Source: Les

nanotechnologies

– Jean-Michel Sallese – Que sais-je ? – 2022

|

|

||

|

Depuis la fin de 2017, les fabricants asiatiques

ont sorti presque simultanément les premiers microprocesseurs gravés en

transistors de 10 et 7 nanomètres ;

c'est-à-dire 10 et 7 milliardièmes de mètre de largeur. Les tout derniers microprocesseurs dépassent 10 milliards de transistors et réalisent plus de 10 000 milliards d'opérations par seconde ! Les Asiatiques fabriquent en ce moment même les

puces A12, gravées en 7 nanomètres, pour le prochain iPhone de septembre

2018, et celui de 2020 serait équipé des puces du taïwanais TSMC gravées en 5 nanomètres. TSMC vient

d'annoncer un investissement de 25 milliards de dollars pour industrialiser

ces microprocesseurs gravés en 5 nanomètres.

|

De son côté, le sud-coréen Samsung a annoncé en

mai dernier la construction d'ici à 2022 d'une usine pour fabriquer des puces

gravées en 3 nanomètres : chaque transistor

fera de 10 à 15 atomes de largeur et sera 30 000 fois plus fin qu'un cheveu. L'investissement pour construire l'usine, qui

sera la plus coûteuse jamais bâtie sur la planète, dépassera 20 milliards de dollars. Présenté le 8 juin 2018, le Summit américain est

désormais l'ordinateur le plus puissant du monde avec ses 122 millions de milliards d'opérations par seconde contre

93 millions de milliards pour le Sunway TaihuLight chinois, qui a perdu la

place de leader. |

|

Source: L'Express - Laurent

Alexandre – 12/07/2018

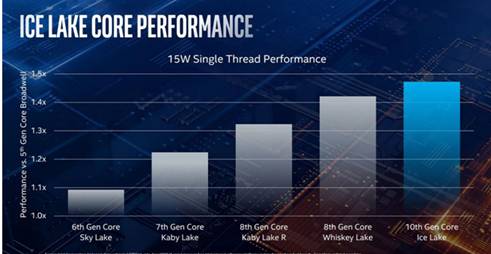

En 2019 (10 nm pour la 10e génération) – Nom de code:

Ice Lake

Microprocesseurs Inter

Core fin 2017

|

Intel Core i9 7980 XE de fin 2017 atteint une épaisseur de gravure de 14

nm (nanomètres

ou millième de microns).

|

Voir 14 nm lithography process –

Wiki / 14 nanometer –

Wikipedia

|

|

||

|

Quelques

nanomètres (nm) d’épaisseur pour la gravure. La taille d’un brin d’ADN ou de

dix atomes de carbone3.

Proche

des 20 milliards de

transistors pour les super-puces en 2017, comme:

Les

usines doivent investir des sommes colossales Conditions:

salle blanche sans poussière, sans vibrations, sans variation de température

ou d'humidité. |

La loi de Moore (doublement du nombre de transistors par puce

tous les deux ans) est toujours d'actualité; certains prédisent qu'elle va

résister jusqu'en 2021. Les puces des Smartphones sont à 14 nm voire

10 nm. Passer à 7 nm nécessite d’investir 500 millions de dollars

rien que pour le design, auxquels il faut ajouter autant pour la fabrication

– D'après Jean-Eric Michallet du CEA Leti. GlobalFoundries et Samsung

préparent avec IBM la gravure en 5 nm d’une puce en 3D atteignant 30 milliards de

transistors. La première puce d'Intel en

1971, le microprocesseur 4004:

|

|

Voir Nombre 20

milliards / Puissance de calcul

D'après: L’infiniment petit se chiffre en milliards de dollars - Le

Monde économie - 04.12.2017 - Charles de Laubier

Voir site – Description

du processeur GV100 sur HARDWARE.FR

![]()

ARCHIVES

|

|

|

|

|

|

Voir Supercalculateur

en 2013

Presse de juin 2013

|

|

|||

|

100 GHz Le transistor le plus rapide en

2010 |

|

||

|

45 nm Prototypes de puce 26 j Intel |

|

||

Presse de février 2007

|

|

|||||||||||||||||||||||||||||||||||||||||||||

|

INTEL

*B |

|||||||||||||||||||||||||||||||||||||||||||||

Sites Internet - février

2007

|

|

|||

|

Fréquence d'horloge Cour Annoncée |

2 à 3 GHz 5 GHz |

|

|

|

Perform Cour Objectif Intel 2010 |

7 à 21 W 0,5 W |

|

|

|

Finesse de l Cour Objectif Intel 2011 |

65 nm 22 nm |

|

|

|

Qu Cour Record en 2007 |

1 milli 1, 7 milli |

|

|

|

Mémoire SDRAM En 2000 – Pentium En 2007 – Penryn |

18 Mbits 153 Mbits |

|

|

|

Mémoire c |

2 Moctets |

|

|

|

Prix des puces |

400 à 1300 $ |

|

|

|

Mémoire DRAM Annoncée en 2007 |

1 Gbits |

|

|

!!! Le seul but de ce t

Les princi

|

AMD Freesc IBM Infineon Intel NEC Renes STMicroelectronics Toshib TS |

|

Intel |

|

début 2006 juillet 2006 |

|

|

Intel |

chacune

dotée de deux cœurs 4

Mo de cache

|

|

|

|

Intel |

|

sept

2006 |

|

|

Electronics |

Utilisation: téléphones mobiles, appareils photo numériques, consoles de jeux portables ou baladeurs multimédias.

|

déc.

2006 |

|

|

AMD |

Modèle

4000: 2,1 GHz Modèle

4400: 2,3 GHz Modèle

4800: 2,5 GHz

Modèle

à 2,8 GHz et à 3 GHz |

déc.

2006 |

|

|

Intel |

|

début

2007 |

|

|

IBM |

Ø

Power 5:

jusqu'à 2,3 GHz - Actuel Ø

Power 6 : 5 GHz -

Commerci Intel annonce 4 GHz Coures

|

début

2007 |

|

|

Intel |

|

j |

|

Intel |

90

nm: en réduction

drastique 65

nm - Conroe: produit phare 45

nm - Penryn: en cours de lancement Du

Conroe

Nec

et Toshiba sont aussi en lice pour la course à la finesse de gravure |

février

2007 |

|

|

|

|

IBM |

|

février

2007 |

|

AMD |

|

juin

2007 |

|

Toshib S |

|

j |

|

Sony Toshib IBM (STI) |

Existait

déjà en 90 nm et 3,2 GHz |

février

2007 |

|

Intel |

|

2

Sem 2008 |

|

Intel |

|

2009 |

|

IBM |

|

2010 |

|

|

||

|

|

|

|

|

|

||

|

Encyclopédie

Brittanica

|

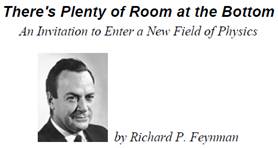

Why cannot we write the

entire 24 volumes of the Encyclopedia Brittanica on the head of a pin? |

|

|

Encyclopédie

Universelle

Calcul

|

||

Voir Bibliothèque

Univers

|

|

|

|

En 1 ns la lumière

parcourt: 30 cm. Cette longueur

est voisine de la taille des circuits électroniques de nos ordinateurs. Ce fait

semble limiter de manière incontournable la vitesse que peuvent atteindre les

ordinateurs. Comparaison:

= 1/2 (0,3)3

/ ( (0,5 10-6)3 x 103 ) = 1/2 27 10-3

/ 0,125 10-18 x 103) = 108 x 1012 = 1014

opérations par seconde.

Voir Puissance de calcul |

|

|

PICOSECONDE - COMMUTATION ÉLECTRONIQUE – vers années 2000 |

|

|

Le fait que le cerveau accomplisse

de nombreuses opérations plus rapidement que les ordinateurs actuels tient,

non pas à la vitesse de ses composantes individuelles mais à la supériorité

de la conception des circuits. Voir Loi de Moore |

|

![]()

|

Suite |

|

|

Aussi |

|

|

Sites |

|

|

Cette page |

![]()

![]()

|

En 1997

En 1998

Celle d'IBM sera pour les générations

suivantes. |

|

CADENCE D'HORLOGE Fréquence et temps

de cycle

Mégahertz

& Gigahertz

100

MHz correspond à 10 nanosecondes de temps de cycle de l'horloge interne.

on

a souvent recourt à un même test exécuté sur les différentes machines (bench

mark)

|

|

Voir |

|

|

|||||||||||||||||||||||||||||||||||||||||

|

Évolution du nombre

de transistors sur une seule puce

microprocesseur Intel

Le

Pentium Pro

En

1997,

En

1998,

La

loi de Gordon Moore Le nombre

de transistors sur une puce double

tous les 18 mois

Gordon

Moore (1928 - )

|

|||||||||||||||||||||||||||||||||||||||||

![]()